# Green Mobile Devices and Networks

Energy Optimization and Scavenging Techniques

Hrishikesh Venkataraman and Gabriel-Miro Muntean, Editors

# Green Mobile Devices and Networks

### Energy Optimization and Scavenging Techniques

Hrishikesh Venkataraman and Gabriel-Miro Muntean, Editors

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business AN AUERBACH BOOK CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2012 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20111020

International Standard Book Number-13: 978-1-4398-5990-2 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright. com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### Contents

| Preface      | vii  |

|--------------|------|

| The Editors  | xi   |

| Contributors | xiii |

#### SECTION I OPTIMIZATION TECHNIQUES

| 1 | Energy Management for Location-Based Services on Mobile Devices3<br>MIKKEL BAUN KJÆRGAARD                             |

|---|-----------------------------------------------------------------------------------------------------------------------|

| 2 | Energy Efficient Supply of Mobile Devices                                                                             |

| 3 | Energy Cost of Software Applications on Portable Wireless Devices53<br>RAJESH PALIT, AJIT SINGH, AND KSHIRASAGAR NAIK |

| 4 | Striking a Balance between Energy Conservation and QoS<br>Provision for VoIP in WiMAX Systems                         |

| 5 | QoE-Based Energy Conservation for VoIP Applications in WLAN 111<br>ADLEN KSENTINI AND YASSINE HADJADJ-AOUL            |

| 6 | Minimum Energy Multicriteria Relay Selection in Mobile Ad Hoc<br>Networks                                             |

| 7 | Energy Optimization Techniques for Wireless Sensor Networks 153<br>SONALI CHOUHAN                                     |

#### SECTION II SCAVENGING TECHNIQUES

| 8  | Design Issues in EM Energy Harvesting Systems                                                                                                |

|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | Energy Scavenging for Magnetically Coupled Communication<br>Devices                                                                          |

| 10 | Mixed-Signal, Low-Power Techniques in Energy Harvesting<br>Systems                                                                           |

| 11 | Toward Modeling Support for Low-Power and Harvesting<br>Wireless Sensors for Realistic Simulation of Intelligent Energy-<br>Aware Middleware |

| 12 | Energy Consumption Profile for Energy Harvested WSNs                                                                                         |

| 13 | Radio Frequency Energy Harvesting and Management for<br>Wireless Sensor Networks                                                             |

### Preface

Wireless communications are evolving rapidly toward "beyond 3rd generation (B3G) and 4G systems." At the same time, multimedia transmissions, video-ondemand, gaming, etc. are becoming increasingly popular among the growing number of users. Additionally, over the past couple of years, the demand for multimedia communications and, particularly, video streaming to handheld mobile devices has grown by leaps and bounds. In particular, it is expected that by 2013, mobile phones and other browser-enabled mobile devices will overtake PCs as the most common access device worldwide. As the technology progresses, wireless devices, such as smartphones, iPhones, PDAs, etc., are offering a large number of soughtafter features to customers and support for increasingly complex applications. With each passing year, the functionality and computing power of mobile devices is increasing exponentially, with more and more applications and communication technologies being added consistently to handheld wireless devices. The data rate required for supporting these services is also increasing significantly. This implies a high power requirement at the transmitting and, especially, the receiving wireless devices. However, there is an annual power improvement of only 6 percent over past years and this has not grown in tune with processing and communication technologies. This has a serious impact on the practical use of the mobile devices, especially when accessing rich media-based services. For example, the battery of an iPhone 4GS lasts a mere five hours during Internet connectivity on a 3G network.

Given the stringent requirements and the current limitations of the battery powering of mobile devices, serious efforts are required not only to improve the battery quality, but also improve the battery life. In order to achieve greater success from mobile technology over the next decades, the concept of battery recharging every one to two days has to be completely revamped. This is, of course, easier said than done. A very important question that needs to be investigated and would challenge the researchers/handset manufacturers/network operators is what kind of improvement in the battery can be achieved without significantly altering the overall performance? This is a very interesting yet a very difficult proposition. Recently, there have been several efforts to optimize the energy consumption in both devices and networks. At the level of a device receiving video content via wireless networks, the content's bit rate, frame rate, and color depth could be altered seamlessly depending on the current battery power status. Such a periodic yet a dynamic adaptive mechanism would significantly optimize the battery consumption. An important thing to ponder is that energy optimization schemes can only reduce the consumption and thereby, increase the battery life by a certain but limited amount. There should be alternate mechanisms that need to be used or proposed in order to improve the self reliance of the devices or at least significantly extend the power in the devices by generating or harvesting energy from the environment. An interesting, but challenging aspect is to look at different energy-harvesting techniques and their adaptability to be used by wireless/mobile devices and networks. In order to achieve this, significant changes have to be made in both the hardware mechanisms and software policies to adapt energy use to user requirements for the tasks at hand and to enable automatic recharge from the environment.

Significantly, at the heart of all the technology platforms and handsets introduced are networking and radio communications, thereby enabling base stations/routers/ devices to support rich media services, regardless of where the users are physically located. With the latest extensive demand for high-speed Internet browsing and multimedia transmissions over the wireless networks, the focus of mobile networking has been mainly on increasing the data rate and, importantly, the system processing capacity. However, recently it has become quite evident that data rate increase and throughput maximization are not the only objectives in the next generation of wireless systems. Tomorrow's networks should be optimized for performance and for energy efficiency as well. A network optimized for both performance and energy implies a very different design and architecture and this is what is needed for high data rate communication to be sustainable in the future. To dramatically reduce the energy consumption of today's wireless networks, a radical new approach needs to be initiated. Hence, the next wave of energy efficient networks will not come simply from more traditional research on single aspects, such as physical layer research, but will require holistic, system-wide, breakthrough thinking that challenges basic assumptions.

Harvesting energy from the environment is an important aspect that can create a significant impact in the working pattern of current wireless networks. Energy harvesting can be done at the transmitters, receivers, routers, etc. However, energy harvesting in networks/base stations, etc. is still in a very nascent stage, as compared to energy harvesting in devices. This is primarily because of two reasons. Firstly, the amount of energy required by the wireless networks is very high and it is not possible to harvest such a large amount of energy at the moment. Secondly, the networks/base stations are located at one place and operated by mobile network operators, which are run by big companies. Hence, it becomes easier to power the base station through the existing electricity grid rather than harvesting energy from the environment. However, at the same time, given the increasing computational complexity and the power requirement of the base stations, extracting energy from the environment to power the operations of the base stations is an extremely relevant issue in the decades to come. In fact, in the sensor network domain, given the critical power requirement, energy harvesting for wireless sensor networks is already being carried out. It is an interesting research challenge to extrapolate the energy-harvesting mechanisms from sensor networks to wireless cellular networks.

Energy harvesting in devices is a relatively easy challenge. This is primarily because of the low power requirement of wireless devices. Further, a wireless device is exposed to different sources of energy in the environment, such as heat, light, mechanical keys, electromagnetic waves, audio, etc. Hence, a holistic approach would be to optimize energy harvesting through each individual mechanism and then integrate these different aspects.

This book is a first of its kind focusing solely on energy management in mobile devices and networks. It provides a detailed insight into the different energy optimization techniques and energy harvesting mechanisms in both wireless devices and networks. A unique aspect of the book is the detailed and integrated coverage of different optimization and energy scavenging techniques by different experts. This has not been dealt with before and offers a unique platform for the readers. The book is divided into two parts. The first part describes various energy optimization techniques, whereas the second part presents the energy-harvesting mechanisms.

The first part has seven chapters that focus on energy optimization techniques. Of these, the first three chapters focus on "energy optimizations in devices," while the next four chapters deal with "energy optimization in wireless networks." Chapter 1 talks about energy management and energy optimization techniques for location-based services in mobile devices. Chapter 2 explains the mechanism for energy efficient supply for mobile devices. Chapter 3 models the energy costs of different applications in wireless devices/handsets and is an extension of their previous proposed work in the same domain. In case of wireless networks, the energy consumption for the components across different wireless networks remain the same. However, the pattern of the energy consumption varies across different types of networks. Given the importance of voice communication in cellular networks, Chapter 4 talks about exploiting on-off characteristics of human speech for energy conservation in WiMAX-based systems. Further, given the amount of voice over Internet protocol (VoIP) IP services, Chapter 5 provides an insight into the quality of experience-based energy conservation techniques for VoIP services in Wireless LAN. Notably, a distributed ad hoc network represents a highly complex network in terms of both implementation and deployment. Hence, Chapter 6 explains the importance of considering multiple criteria (minimum energy, multiple relay, etc.) in a mobile ad hoc network and extends their previous work in this field. Above all, given the amount of energy optimization techniques already developed for wireless

sensor networks, Chapter 7 provides a comprehensive overview of energy optimization in wireless sensor networks and how it could be potentially extrapolated for a generic wireless network.

The second part of the book includes six chapters that focus on energy harvesting techniques. Given the importance and the amount of research work being carried out for energy harvesting in wireless devices, four out of the six chapters in this section are dedicated to factors and mechanisms for different energy harvesting solutions for wireless devices. The last two chapters talk about common energy harvesting techniques in wireless networks. Chapter 8 evaluates CMOS RF DC rectifiers for electromagnetic energy harvesting in mobile devices. Further, Chapter 9 explains in detail energy scavenging techniques using a magneto inductive method, while Chapter 10 discusses the mixed signal low power techniques in energy harvesting systems. In Chapter 11, we look at designing wireless sensors with intelligent energy-aware middleware and how could this be extrapolated into futuristic wireless devices. Similarly, the last two chapters of the book, Chapter 12 and Chapter 13, provide an energy consumption profile for energy harvested wireless sensor networks and radio frequency energy harvesting/management for wireless sensor networks, respectively.

Green Mobile Devices and Networks: Energy Optimization and Scavenging Techniques can serve as a benchmark for postgraduates, future engineers, and designers in developing energy-optimal solutions and at the same time provide a deeper insight for the next generation of researchers to harvest energy from the environment for developing the next generation telecommunication systems.

The editors would like to wish the audience a happy reading time and would be happy to receive any queries from the readers.

Hrishikesh Venkataraman Gabriel-Miro Muntean

## The Editors

Hrishikesh Venkataraman, PhD, is a senior researcher and Enterprise Ireland (EI) principal investigator with Performance Engineering Laboratory at the Irish national research center-The RINCE Institute, at Dublin City University (DCU), Ireland. He obtained his PhD from Jacobs University Bremen, Germany, in 2007, for his research on wireless cellular networks. He obtained his master's degree from Indian Institute of Technology (IIT) in Kanpur, India, in 2004, and did his master's thesis from Vodafone Chair for Mobile Communications, Technical University Dresden, Germany, in 2003–2004 under the Indo-German DAAD (Deutscher Akademischer Austausch Dienst) Fellowship. His research interests include mobile multimedia, wireless communications, and energy in wireless. Dr. Venkataraman has published

more than 30 papers in journals, international conferences, and book chapters, and has won a Best Paper Award at an international conference at the University of Berkeley, California, in October 2009. Currently, Dr. Venkataraman is an executive editor of *European Transactions on Telecommunications (ETT)* and is a founding member of the UKRI (United Kingdom/Republic of Ireland) chapter of the IEEE (Institute of Electrical and Electronics Engineers) Vehicular Technology Society.

Gabriel-Miro Muntean, PhD, has established a strong track record in the areas of quality-oriented and performance-aware adaptive multimedia streaming and data communications in heterogeneous wireless environments. Dr. Muntean has been the co-director of a 10-person research laboratory since 2003, which is a state-of-theart facility at the Dublin City University (DCU) Engineering building and well equipped for multimedia delivery research. He has successfully supervised three PhD and three masters for research students, and is currently supervising seven postgraduate researchers and one postdoctoral researcher. Dr. Muntean has received more than 1 million Euro of funding, having been principal investigator on two EI (Enterprise

Ireland), one SFI (Science Foundation Ireland), and five IRCSET (Irish Research Council for Science, Engineering, and Technology) grants and collaborator on two other major Irish grants. In addition, he has been leading Samsung- and Microsoft-funded research projects. Dr. Muntean has authored one book, edited two, and has published five book chapters as well as 25 journal articles and more than 60 conference papers. He has been awarded four Best Paper Awards and is an associate editor for *IEEE Transactions on Broadcasting*.

## **The Contributors**

**Dr. Mehran Abolhasan** is a senior lecturer at the School of Computing and Communications within the faculty of Engineering and Information Technology (FEIT) at the University of Technology Sydney. He has authored over 50 international publications and has won over one million dollars in research funding over the past 5 years. His current research interests are in Wireless Mesh, 4th Generation Cooperative Networks and Body Area and Sensor networks.

Prof. Johnson Ihyeh Agbinya (PhD La Trobe University) is an associate professor of Remote Sensing Systems Engineering at La Trobe University in Melbourne Australia. He also is Professor (Extraordinaire) of Computer Science at the University of the Western Cape, Cape Town and Professor (Extraordinaire) of telecommunication at Tshwane University of Technology (French South African Technical Institute) Pretoria, South Africa. He was Principal Engineer at Vodafone Australia from 2000 to 2003 managing Vodafone Australia research in mobile communications. Prior to that, he was a Senior Research Scientist at CSIRO Division of Telecommunications and Industrial Physics (CSIRO ICT) from 1993 to 2000. At CSIRO he focused on biometric R&D, specifically, face, voice and palm print recognition and compression systems including VoIP. He is widely published with more than 200 peerreviewed authored and co-authored journal and conference papers and six technical books in telecommunications and sensing. He is the Editor of the African Journal of Communication and Information Technology (AJICT) and its founder. He is also founder of various conferences including Auswireless, BroadCom and IB2Com and international committee member of the International Conference on Mechatronics, SETIT and AfroCom. His current research interests include remote and short range communications and sensing, nano-networks and applications of metamaterials in electronic communications and radar, personal area networks, inductive embedded medical devices and wireless power transfer.

**Prof. Li-Minn Ang** is currently with the Centre for Communications Engineering Research at Edith Cowan University. He received his PhD and Bachelor degrees from Edith Cowan University, Australia in 2001 and 1996 respectively. He was

a lecturer at Monash University (Malaysia Campus) and Associate Professor at Nottingham University (Malaysia Campus). His research interests are in the fields of visual information processing, embedded systems and wireless sensor networks.

Dr. Yassine Hadjadj Aoul is an associate professor at the University of Rennes 1, France, where he is also a member of the IRISA Laboratory. He received a B.Sc. In computer engineering with high honors from Mohamed Boudiaf University, Oran, Algeria, in 1999. He received his Master's and PhD degrees in computer science from the University of Versailles, France, in 2002 and 2007, respectively. He was an assistant professor at the University of Versailles from 2005 to 2007, where he was involved in several national and European projects such as NMS, IST-ATHENA, and IST-IMOSAN. He was also a post-doctoral fellow at the University of Lille 1 and a research fellow, under the EUFP6 EIF Marie Curie Action, at the National University of Dublin, where he was involved in the DOM'COM and IST-CARMEN projects, which aim at developing mixed Wi-Fi/WiMAX wireless mesh networks to support carrier grade services. His main research interests concern the fields of wireless networking, multimedia streaming, congestion control and QoS provisioning, and satellite communications. His work on multimedia and wireless communications has led to more than 25 technical papers in journals and international conference proceedings.

Prof. Labros Bisdounis was born in Agrinio, Greece, in 1970. He received the Diploma and PhD degrees in Electrical Engineering both from the Department of Electrical and Computer Engineering, University of Patras, Greece, in 1992 and 1999, respectively. From 2000 until mid-2008 he was with the Research & Development Division of INTRACOM S.A. (INTRACOM TELECOM S.A. since January 2006), Athens, Greece, working as a project manager of European and national research projects regarding the design and development of VLSI circuits and embedded systems for telecom applications. Currently, he is an associate professor and the head in Electrical Engineering Department of Technological Educational Institute of Patras, Greece and the head of the Electronics and Measurements Technology laboratory of the department. In addition, starting from September 2007, he is with the School of Science and Technology of the Hellenic Open University as an external tutor. His main research interest is on various aspects of electronic circuits and systems such as: low-power and highspeed digital circuits and embedded systems design, system-on-chip design, CMOS circuits timing analysis and power dissipation modeling, sensors. Prof. Bisdounis is an author of more than 25 papers in international journals and conferences, as well as of book chapters, teaching notes and technical reports on the above-mentioned areas, and has received more than 350 citations. He is a member of IEEE (Institute of Electrical & Electronic Engineers) and Technical Chamber of Greece.

**Sonali Chouhan** received her PhD degree in Electrical Engineering from the Indian Institute of Technology Delhi, India, in 2009. Since March 2010 she has been with the department of Electronics and Electrical Engineering at Indian Institute of Technology Guwahati, India, where currently she is an Assistant Professor. Her research interests include wireless sensor networks, error control codes, energy optimization, embedded systems, and genetic algorithms. Recently, Dr. Chouhan received the Microsoft Outstanding Young Faculty award in 2010.

**Prof. Gianluca Cornetta** obtained his MSc Degree from Politecnico di Torino (Italy) in 1995 and his PhD from Universidad Politécnica de Cataluña (Spain) in 2001 both in Electronic Engineering. In 2003 he joined Universidad CEU-San Pablo in Madrid (Spain) where he is presently an associate professor. Prior to joining Universidad CEU-San Pablo, he has been a lecturer in the Departement of Electronic Engineering of Universidad Politécnica de Cataluña (Spain), a digital designer at Infineon Technologies Gmbh (Germany), and an ICT consultant at Tecsidel SA (Spain) in the field of real-time embedded systems. In 2004 he founded the Department of Electronic System Engineering and Telecommunications that he chaired until February 2008. He is also a research fellow at the Vrije Universiteit Brussel and an invited professor at the Institut Superieur d'Electronique de Paris (ISEP) where he teaches wireless system design in the Advances in Communication Environment (ACE) Master. His current research interests include RF circuit design for wireless sensor networks with special emphasis on IEEE 802.15.4 (ZigBee), digital communication circuits, software radio, and distributed real-time embedded systems.

**Prof. Swades De** received his BTech in Radiophysics and Electronics from the University of Calcutta, India, in 1993, MTech in Optoelectronics and Optical Communication from the Indian Institute of Technology (IIT) Delhi, in 1998, and PhD in Electrical Engineering from the State University of New York at Buffalo, in 2004. Before moving to IIT Delhi in 2007, where he is currently an Associate Professor of Electrical Engineering, he was an Assistant Professor of Electrical and Computer Engineering at NJIT (2004–2007). He also worked as a post-doctoral researcher at ISTI-CNR, Pisa, Italy (2004), and has nearly five years industry experience in India in telecommunication hardware and software developments (1993–1997, 1999). His research interests include performance study, resource efficiency in multihop wireless and high-speed networks, broadband wireless access, and communication and systems issues in optical networks.

**Mr. Komlan Egoh** received his diplome d'ingenieur in Electrical Engineering from the Ecole Nationale Supérieure d'Ingénieurs in 2001 at the University of Lome in Togo. In 2005 he received his MS degree in Internet Engineering from the department of Electrical and Computer Engineering at the New Jersey Institute of Technology. He is currently a PhD candidate in the same department. His

research is in the general areas of communication networks, wireless mesh and ad hoc sensor networks. From 2001 to 2004, and 2007-2008, he has work software engineer in various technology companies in Europe, Africa and North America.

**Dr. Nikolaos Fragoulis** received his BSc degree in Physics in 1995, his MSc in Electronics & Computer Science in 1998 and the PhD in Microelectronics in 2005, all from the Electronics Laboratory (ELLAB), Dept. of Physics, University of Patras (UoP), Greece. He has worked as postdoctoral researcher or project manager in several national and European-funded R&D projects, in the fields ofmicroelectronics, analogue and digital signal processing. He has worked in the private sector as a software engineer and as a silicon-based systems engineer. Dr Fragoulis has authored or co-authored more than 30 journal and conference papers, and 3 book chapters. He is currently Vice President of technology in IRIDA Labs, Ltd., Greece.

**Mr. Philipp M. Glatz** received his BS and MS in Telematics specializing in System-on-Chip-Design and Computational Intelligence from Graz University of Technology, Austria, in 2005 and 2007, respectively. As a university assistant with the Institute for Technical Informatics at Graz University of Technology, Austria, he is assigned research and teaching duties. Currently, he is a PhD candidate in electrical and computer engineering. His research interests include wireless sensor network middleware and power awareness with a focus on network coding, energy harvesting with a focus on energy efficiency and measurement systems as well as tool chain and development environment integration. He is a member of the Institute of Electrical and Electronics Engineers and is author and co-author of more than 20 publications.

**Mr. Leander B. Hörmann** is a PhD candidate in electrical and computer engineering at the Institute for Technical Informatics, Graz University of Technology, Austria. As a university assistant at this institute, he teaches undergraduates and conducts research. He received his BSc and Dipl-Ing in Telematics specializing in Technical Informatics and Autonomous Robots from Graz University of Technology, Austria, in 2008 and 2010, respectively. His research interests include system architecture of energy harvesting wireless sensor networks, low power techniques and the simulation of software and hardware. He is a member of the Institute of Electrical and Electronics Engineers.

**Prof. H. S. Jamadagni** received his bachelors degree in Electrical Engineering from Bangalore University, India in 1970. In 1972 he received ME degree and PhD in 1986 degrees from Indian Institute of Science, Bangalore, India. From 1972 to 1974 he was a Deputy Engineer at Indian Telephone Industries (ITI), Bangalore. From 1974 onwards he is associated with the Indian Institute of Science and has been a professor since 2001. He was appointed as the Chairman, Centre for Electronics Design and Technology (CEDT) IISc in 1996. He served

as its chairman until June 2009. He is Principal Investigator (PI) in several major National and International collaboration and sponsored research projects including a few European Union (EU) Framework projects. His research interests are Telecom, VLSI, embedded systems, wireless sensor networks, pedagogy, energy harvesting, cognitive radio, E-Learning, and technologies for wildlife conservation. Currently, he is a member of Telecom Regulatory Authority of India.

**Dr. Mikkel Baun Kjærgaard** is a postdoctoral researcher at the Department of Computer Science in Aarhus University, Denmark. His current research interests are within the area of pervasive positioning: positioning anywhere, anytime, of anything. His interests spans from innovative applications within this area to technical challenges such as energy efficiency. He holds a PhD in Computer Science from Aarhus University based on research on indoor positioning using radio location fingerprinting.

**Dr. Adlen Ksentini** received the MS degree in telecommunications and multimedia networking from the University of Versailles and the PhD degree in computer science in 2005 from the University of Cergy, Pontoise. His PhD dissertation focused on QoS provisioning in IEEE 802.11-based networks. Since 2006, he is an associate professor at the University of Rennes 1, France, and member of the IRISA Laboratory. His research interests include QoS and QoE support for multimedia content, congestion control in LTE and Green Networks. He is a coauthor of more than 20 technical journal papers and international conference proceedings. He is a member of the IEEE.

**Prof. Xiao-Hui Lin** received his BS and MS degrees in Electronics and Information Science from the Lanzhou University, in 1997 and 2000, respectively. He got his PhD degree in Electrical and Electronic Engineering from the University of Hong Kong in 2003. He is now an associate professor in the Faculty of Information Engineering, Shenzhen University in Guangdong, China. His research interests include mobile computing, wireless networking, and multimedia communication. In these fields, he has published more than 40 papers in international leading journals and refereed conferences.

**Ms. Ling Liu** received her BS in Electronic Engineering from Shenzhen University in 2008. After that, she began her MS study in the same university. She is expected to get her MS degree in telecommunication systems in 2011. She is now a system engineer in UTStarcom, Shenzhen. Her research interests include wireless networks, signal processing and information theory.

**Ms. Mehrnoush Masihpour** completed her BS degree in Computer Sciences from University of Najafabad, Esfahan in Iran in 2007 and the Graduate Certificate in Telecommunication Networking from University of Technology, Sydney in

#### xviii The Contributors

Australia in 2009. She started her PhD at the University of Technology, Sydney in 2009. Her research interests are wireless communication networks, magnetic induction communication, personal area network and cooperative communications in mobile networks. She has authored 14 international publications. She also has been involved in the industry for more than three years.

**Prof. Kshirasagar Naik** is an associate professor in the Department of Electrical and Computer Engineering at the University of Waterloo. His current research interests include energy cost modeling and analysis of smartphones, energy cost modeling and analysis of cloud computing architectures, wireless communication systems, intelligent transportation systems, vehicular networks, sensor networks, communication protocols, and application software. He has published numerous research articles in high quality international conferences and journals. He is a co-author of a textbook entitled "Software Testing and Quality Assurance: Theory and Practice" published by John Wiley in 2008. His second book entitled "Software Evolution and Maintenance" will be published by John Wiley in April 2012. He is on the program committees of several IEEE international conferences.

Dr. Ignas G. M. M. Niemegeers got a degree in Electrical Engineering from the University of Gent, Belgium, in 1970. In 1972 he received a MScE degree in Computer Engineering and in 1978 a PhD degree from Purdue University in West Lafayette, Indiana. From 1978 to 1981 he was a designer of packet switching networks at Bell Telephone Mfg. Cy, Antwerp, Belgium. From 1981 to 2002 he was a professor at the Computer Science and the Electrical Engineering Faculties of the University of Twente, Enschede, The Netherlands. From 1995 to 2001 he was Scientific Director of the Centre for Telematics and Information Technology (CTIT) of the University of Twente, a multi-disciplinary research institute on ICT and applications. Since May 2002 he holds the chair Wireless and Mobile Communications at Delft University of Technology, where he is heading the Centre for Wireless and Personal Communication (CWPC) and the Telecommunications Department. He was involved in many European research projects, e.g., the EU projects MAGNET and MAGNET Beyond on personal networks, EUROPCOM on UWB emergency networks and, eSENSE and CRUISE on sensor networks. He is a member of the Expert group of the European technology platform eMobility and IFIP TC-6 on Networking. He is also chairman of the HERMES Partnership, an organization of leading European research institutes and universities in telecommunications. His present research interests are 4G wireless infrastructures, future home networks, ad-hoc networks, personal networks, cognitive networks.

**Mr. Rajesh Palit** received his BS degree in Computer Science and Engineering from Bangladesh University of Engineering and Technology (BUET), and MS degree in Computer Engineering from University of Manitoba in 2000 and 2004, respectively. He is now a PhD candidate in the Department of Electrical and

Computer Engineering at University of Waterloo, Canada. He also served 2 years in industry and 2 years in academia as a faculty member in North South University, Dhaka, Bangladesh. His current research interests include energy efficient wireless networks, pervasive and green computing.

Prof. S. R. S. Prabaharan is currently a full professor of Electronics in the University of Nottingham in its Malaysia Campus. Prabaharan graduated from The American College, an autonomous affiliate of Madurai Kamaraj University, India and all of his degrees are from Madurai Kamaraj University. He earned his PhD in Solid State Devices in 1992. He has worked at CSIR research labs (National Aerospace Laboratory) in Bangalore, India on Ionic/electronic devices using Raman spectroscopy, CECRI, another CSIR research lab in Karaikudi, India. Later, he became a Research Scientist under DST (Department Science and Technology) Young Scientist Research Award program. He also taught at Universiti Malaya, Malaysia and later joined the Applied Sciences Faculty at Universiti Teknologi Petronas. In 1999, he joined the Faculty of Engineering, Multimedia University as a Senior Lecturer before moving to The University of Nottingham Malaysia Campus as an Associate Professor. Dr Prabaharan has been invited as visiting Senior Fellow/Scientist in different academic institution to foster research and initiate joint research activities with academic/research institutions which include: UPMC, Paris (1998) and Tokyo Institute of Technology; Japan (2003), Southern University, USA (2005) and University of Sheffield, UK (February 2006). He is also a visiting research consultant to Southern University, Baton Rouge, USA where he was invited under US Army Research Project. He is a peer reviewer for numerous international journals published by Elsevier, Springer and Hindawi, and has been the guest editor for a Solid State journal published by Springer (in press, 2007). His research interest are in the field of supercapacitors; hybrid power sources; lithium-ion batteries; nanotechnology of clean energy; solid state devices; semiconductor gas sensors; modeling and simulation of power electronic circuits (UPS, Mini power grids and Solar PV MPP devices); supercapacitors for power assist applications.

**Dr. T. V. Prabhakar** received his Bachelors degree in Science from Bangalore University, India in 1983. In 1987 he received MSc (Physics) degree, and obtained MSc (Engg) degree in 2004 from Indian Institute of Science (IISc), Bangalore, India. He joined IISc in 1985 and served in various capacities. He is currently a Senior Scientific Officer in Centre for Electronics Design and Technology (CEDT), IISc, Bangalore. He is the founder member of the Zero Energy Networks (ZEN) laboratory in CEDT. He is serving as a technical lead in several National and International collaboration sponsored research projects. Some of the areas include Telecom, Embedded systems, Wireless sensor networks and Education projects. He is associated with many Industrial Research/Developments projects in the areas related to Wireless sensor networks, Embedded systems, and Energy harvesting.

His present research interests are Communication networks, Wireless networks, Energy harvesting Wireless sensor networks, Embedded systems and application of technology for development application of technology for development application of technology for development.

Dr. R Venkatesha Prasad received his bachelors degree in Electronics and Communication Engineering and MTech degree in Industrial Electronics from University of Mysore, India in 1991 and 1994. He received a PhD degree in 2003 from Indian Institute of Science, Bangalore, India. During 1996 he was working as a consultant and project associate for ERNET Lab of ECE at Indian Institute of Science. While pursuing the PhD degree, from 1999 to 2003 he was also working as a consultant for CEDT, IISc, Bangalore for VoIP application developments as part of Nortel Networks sponsored project. In 2003 he was heading a team of engineers at the Esqube Communication Solutions Pvt. Ltd. Bangalore for the development of various real-time networking applications. Currently, he is a part-time consultant to Esqube. From 2005 till date he is a senior researcher at Wireless and Mobile Communications group, Delft University of Technology working on the EU funded projects MAGNET/MAGNET Beyond and PNP-2008 and guiding graduate students. He is an active member of TCCN, IEEE SCC41, and reviewer of many Transactions and Journals. He is on the TPC of many conferences including ICC, GlobeCom, ACM MM, ACM SIGCHI, etc. He is the TPC co-chair of CogNet workshop in 2007, 2008 and 2009 and TPC chair for E2Nets at IEEE ICC-2010. He is also running PerNets workshop from 2006 with IEEE CCNC. He is the Tutorial Co-Chair of CCNC 2009 & 2011 and Demo Chair of IEEE CCNC 2010. He is an invited member of IEEE ComSoc Standards Board.

Prof. Roberto Rojas-Cessa received the M Comp Eng degree and the PhD degree in Electrical Engineering from Polytechnic Institute of New York University, Brooklyn, NY. He also received an MSc degree in Electrical Engineering from the Research and Advanced Studies Center (CIVESTAV), Mexico. He received his BS in Electronic Instrumentation from Universidad Veracruzana, Mexico. Currently, he is an associate professor in the Department of Electrical and Computer Engineering, New Jersey Institute of Technology, Newark, NJ. He was an adjunct professor and a research associate in the Department of Electrical and Computer Engineering of Polytechnic Institute of New York University. He has been involved in design and implementation of application-specific integrated-circuits (ASIC) for biomedical applications and high-speed computer communications, and in the development of high-performance and scalable packet switches and reliable switches. He was part of the team designing a 40 Tb/s core router in Coree, Inc., in Tinton Falls, NJ. His research interests include high-speed switching and routing, fault tolerance, qualityof-service networks, network measurements, and distributed systems. He was a visiting professor in Thammasat University, Rangsit Campus, Thailand, in 2010. His research has been funded by U.S. National Science Foundation and Industry.

He was the recipient of the Advance in Research Excellence of the ECE Dept. in 2004. He has served in several technical committees for IEEE conferences and as a reviewer for several IEEE journals. He has been a reviewer and panelist for U.S. National Science Foundation and the U.S. Department of Energy. He has more than 10 years of experience in teaching Internet protocols and computer communications. Currently, he is the Director of the Networking Research Laboratory at the ECE Department and the Coordinator of the Networking Research Focus Area Group of the same department.

**Prof. David J. Santos** obtained his MSc and PhD Degrees both from Universidad de Vigo, Spain (in 1991 and 1995 respectively). From 1995 to 2005 he has been a professor at Universidad de Vigo and a visiting scholar to University of Rochester (USA) and University of Essex (UK). Since 2005 he is an associate professor at Universidad CEU-San Pablo in Madrid (Spain) where he also chairs the Division of Engineering of the Escuela Politécnica Superior. His research interests include: quantum information processing, quantum optics, optical communications, communication circuits, and applied mathematics problems related with process modelling and optimisation, and data mining.

**Prof. Kah Phooi Seng** received her PhD and Bachelor degree (first class honors) from University of Tasmania, Australia in 2001 and 1997 respectively. She is currently an associate professor in the School of Electrical & Electronic Engineering at The University of Nottingham Malaysia Campus. Her research interests are in the fields of intelligent visual processing, biometrics and multi-biometrics, artificial intelligence and signal processing.

**Prof. Ajit Singh** received the BSc degree in electronics and communication engineering from the Bihar Institute of Technology (BIT), Sindri, India, in 1979 and the MSc and PhD degrees from the University of Alberta, Edmonton, AB, Canada, in 1986 and 1991, respectively, both in computing science. From 1980 to 1983, he worked at the R & D Department of Operations Research Group (the representative company for Sperry Univac Computers in India). From 1990 to 1992, he was involved with the design of telecommunication systems at Bell-Northern Research, Ottawa, Canada. He is currently an associate professor at Department of Electrical and Computer Engineering, University of Waterloo, Waterloo, ON, Canada. His research interests include network computing, software engineering, database systems, and artificial intelligence.

**Prof. Dr. Christian Steger** received 1990 the Dipl-Ing degree (equivalent to the American Master of Science) and 1995 the Dr. Techn. degree (equivalent to the American PhD degree) in Electrical Engineering, Graz University of Technology, Austria. Graduated from Export, International Management and Marketing course

in June 1993 at Karl-Franzens-University of Graz. From 1989 to 1991 Software Trainer and Consultant at SPC Computer Training Ges.m.b.H., Vienna. From 1990 to 1991 research engineer at the Institute for Technical Informatics, Graz University of Technology. Since 1992 he is an assistant professor at the Institute for Technical Informatics, Graz University of Technology. In summer 2002 he was a visiting researcher at the Department of Computer Science at the University College Dublin (Ireland). He heads the HW/SW co-design group (8 PhD students) at the Institute for Technical Informatics. His research interests include embedded systems, HW/SW co-design, HW/SW co-verification, SOC, power awareness, smart cards, UHF RFID systems, multi-DSPs. He is currently working with industrial partners on heterogeneous system design tools for system verification and power estimation/optimization for RFID systems, smart cards and wireless sensor networks. Christian Steger has supervised and co-supervised over 73 master's thesis and co-supervised 8 PhD students, and published more than 70 scientific papers as author and co-author. He is member of the IEEE and member of the ÖVE (Austrian Electro-technical Association). He was member of the organizing committee of the Telecommunications and Mobile Computing Conference 2001, 2003, and 2005.

**Dr. Christos Theoharatos** was born in Athens in 1973. He received a BSc degree in Physics in 1998, an MSc degree in Electronics & Computer Science in 2001, and a PhD degree in Image Processing and Multimedia Retrieval in 2006, all from the Electronics Laboratory (ELLAB), Dept. of Physics, University of Patras (UoP), Greece. He is currently and R&D manager for IRIDA Labs. He is also involved as a Post-Doc researcher to the Digital Information Processing group, at ELLAB – UoP. During the last five years he has been acting as a Technical Manager in a number of European and National R&D projects in the fields of signal and image processing, multimedia services and information technology. He has published more than 30 journal and conference papers in the fields of his expertise. His main research interests include pattern recognition, multimedia databases, image processing and computer vision, data mining, and graph theory.

**Prof. Abdellah Touhafi** obtained his MSc Degree in Electronic Engineering from Vrije Universiteit Brussel (Belgium) in 1995 and his PhD from the Faculty of Engineering Sciences from Vrije Universiteit Brussel (Belgium) in 2001. In 2001 he became post-doctoral researcher at Erasmushogeschool Brussel where he researched on environmental monitoring systems. In 2003 he became professor and founded his research group on reconfigurable and embedded systems. Since 2009 he is the program coordinator in the Industrial Sciences Department. His current research interests include embedded real-time systems, high performance and reconfigurable computing, Sensor Webs for localization and environmental monitoring, security, Software Defined Radio and digital communication circuits.

**Dr. José Manuel Vázquez** obtained his MSc and PhD Degrees both from Universidad Politécnica of Madrid. He has over thirty years experience in the IT sector, designing and developing a variety of innovative projects for marketleading companies. During his career he has played different roles and positions of responsibility in various areas of business for which he worked such as production, sales, marketing, communication and R&D. He is currently a lecturer at University CEU-San Pablo in Madrid and managing partner of a consultancy company focused on the implementation of change management and BPR for new companies in the digital economy. It has also been evaluating research projects of the European Union and has served on various national and international committees related to marketing and regulation in the field of IT.

Prof. Dr. Reinhold Weiss is professor of Electrical Engineering (Technical Informatics) and head of the Institute for Technical Informatics at Graz University of Technology, Austria. He received the Dipl-Ing degree, the Dr-Ing degree (both in Electrical Engineering) and the Dr-Ing habil degree (in Realtime Systems) from the Technical University of Munich in 1968, 1972 and 1979, respectively. In 1981 he was as a visiting scientist with IBM Research Laboratories in San Jose, California. From 1982 to 1986 he was professor of Computer Engineering at the University of Paderborn (Germany). He is author and co-author of about 170 scientific and technical publications in Computer Engineering. For E&I (Elektrotechnik & Informationstechnik, Springer-Verlag) he served several times as a guest editor for special issues on Technical Informatics and Mobile Computing, respectively. In 2001 and 2003 he organized two Workshops on Wearable Computing. His research interests focus on Embedded Distributed Real-Time Architectures (parallel systems, distributed fault-tolerant systems, wearable and pervasive computing). He is a member of the International Editorial Board of the US- journal "Computers and Applications" (ISCA). Further, he is a member of IEEE, ACM, GI (Gesellschaft für Informatik, Germany), and ÖVE (Österreichischer Verein für Elektrotechnik, Austria).

**Mr. Adamu Murtala Zungeru** received his BEng degree in Electrical and Computer Engineering from the Federal University of Technology (FUT) Minna, Nigeria in 2004, and MSc degree in Electronics and Telecommunication Engineering from the Ahmadu Bello University (ABU) Zaria, Nigeria in 2009. He is a Lecturer Two (LII) at the Federal University of Technology Minna, Nigeria in 2005-to date. He is a registered engineer with the Council for the Regulation of Engineering in Nigeria (COREN), and member of the Institute of Electrical and Electronics Engineers (IEEE). He is currently a PhD candidate in Electrical and Electronics Engineering at the University of Nottingham Malaysia Campus. His research interests include Energy Efficient routing, Energy harvesting, Storage and Management in Wireless and Visual Sensor Networks.

### Chapter 10

### Mixed-Signal, Low-Power Techniques in Energy Harvesting Systems

### N. Fragoulis, L. Bisdounis, V. Tsagaris, and C. Theoharatos

#### Contents

| 10.1 | Introduction                                            | 256 |

|------|---------------------------------------------------------|-----|

| 10.2 | Mixed-Signal Environment in Energy Harvesting Systems   |     |

|      | 10.2.1 Microsensor Wireless Networks                    |     |

|      | 10.2.2 Radio Frequency Identification (RFID)            | 258 |

| 10.3 | Low Power Techniques in Digital Design                  | 259 |

|      | 10.3.1 Reducing Power in Digital Circuits               |     |

| 10.4 | Low Power Techniques in Analog Design                   |     |

|      | Comparison of the Power Consumption of Analog           |     |

|      | and Digital Circuits                                    |     |

| 10.6 | Combination of Techniques Toward Low-Voltage,           |     |

|      | Mixed-Signal Design                                     |     |

| 10.7 | Optimum Combination of Analog                           |     |

|      | and Digital Low-Power Techniques                        |     |

|      | 10.7.1 Instantaneous Companding Technique               |     |

|      | 10.7.2 Subthreshold CMOS Design                         |     |

| 10.8 | Power-Oriented Electronic Design Automation (EDA) Tools |     |

|      | 10.8.1 Transistor Level Tools                           |     |

| 10.8.2 Gate-Level or Logic-Level Tools            | 73 |

|---------------------------------------------------|----|

| 10.8.3 Register Transfer-Level Tools              |    |

| 10.8.4 Behavioral-Level Tools and Power Emulation |    |

| 10.9 Conclusions                                  |    |

| References                                        |    |

#### **10.1 Introduction**

Energy harvesting systems pose a new challenge in the domain of circuit design because they must operate with an extremely low-power budget. As is evident, a circuit functioning in such an energy-starving environment must be operated near the fundamental low-power limits and should be designed on the basis of very strict guidelines conforming to the most recent advances in low-voltage and low-power design.

Modern portable systems, which are the main application field of energy harvesting techniques, are mainly mixed-signal systems comprised of a digital core including, amongst others, a central processing unit (CPU) or digital signal processing (DSP) and memory, often surrounded by several analog interface blocks, such as I/O (input/output), D/A (digital-to-analog), and A/D (analog-to-digital) converters, RF (radio frequency) front ends, and more. Therefore, a mobile device is a characteristic example of a mixed-signal system, which is, namely, a system that combines, to some extent, analog and digital circuitry.

The evolution in complementary metal oxide semiconductor (CMOS) technology, which is the dominant technology in portable systems, is motivated by the decrease in the price-per-performance factor for digital circuitry in a pace dictated by Moore's Law, the main effect of which is the shrinking of the dimensions (feature size) of the devices. To ensure sufficient lifetime for digital circuitry and to keep power consumption at an acceptable level, this dimension-shrink is accompanied by lowering of nominal supply voltages. While this evolution in CMOS technology is by definition very beneficial for digital circuits, this is not the case for analog circuits. In addition, although low-power techniques for analog and digital circuits have nowadays sufficiently matured, there still remain some fundamental controversies regarding the design of a mixed-signal system that a designer must take under consideration.

The most efficient way to reduce the power consumption of digital circuits is to reduce the supply voltage, since the average power consumption of CMOS digital circuits is proportional to the square of the supply voltage. On the other hand, the reduction of the supply voltage is also mandatory due to dimension shrinking in order to maintain the electric field at an acceptable level.

The rules for analog circuits seem to be different than those applied to digital circuits. This is mainly due to the fact that the power consumption of analog circuits at a given temperature is basically set by the required signal-to-noise ratio (SNR) and the required bandwidth. A very important technique that seems to bridge the controversies between analog and digital low-power techniques is based on the ability of CMOS transistor devices to work in the *subthreshold region (weak inversion)*. CMOS transistors functioning in this region exhibit extremely low power consumption, as a result of extremely low operating current densities that are inherent in the subthreshold operation. Subthreshold operation is not suitable for applications where high performance is needed, but seems a very attractive solution in energy harvesting systems where simple systems are generally implemented.

In the rest of this chapter, the particularities of the low-power design in the digital and the analog domain will be analyzed in order for the reader to gain a deeper knowledge of the effects that specific design choices have on the power performance in the analog and the digital world. In addition, new design techniques will be analyzed and discussed that bridge the analog and digital world controversies toward a successful, mixed-signal, ultralow-power design, suitable for use in an energy harvesting application. Finally, a brief review of the power-aware electronic design automation (EDA) software tools available in the market will be conducted in order to give to the reader a brief guide of the available means for analog and digital low-power design.

#### 10.2 Mixed-Signal Environment in Energy Harvesting Systems

Typical applications of energy harvesting systems are small, wireless autonomous devices, like those used in wireless microsensor networks and radio frequency identification Systems (RFIDs). These types of applications would benefit from unbounded lifetimes in an environment where changing batteries is impractical or impossible, since the concept of energy harvesting involves converting ambient energy from the environment into electrical energy to power the circuits or to recharge a battery. Microsensor nodes must keep average power consumption in the 10 to 100  $\mu$ W range to enable energy harvesting [1]–[3]. Combining energy harvesting techniques with some form of energy storage can theoretically extend system lifetimes indefinitely. Clearly, this type of system will be much more effective when coupled with the significant power and energy savings made possible by applying power reduction design techniques to their individual components.

#### 10.2.1 Microsensor Wireless Networks

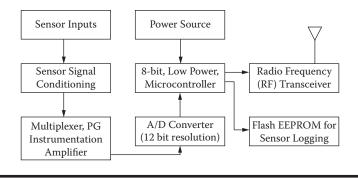

A microsensor node refers to a system that provides sensing, computation, and communication functionality. The block diagram of a typical microsensor node is shown in Figure 10.1. Wireless microsensor networks consists of tens to thousands of distributed nodes that sense and process data and relay the results to the end

Figure 10.1 A block diagram of a typical wireless microsensor node.

user. Proposed applications for microsensor networks include habitat monitoring, structural health monitoring, and automotive sensing [3] [4].

The performance requirements for microsensor nodes in these applications are very low. The rate at which data changes for environmental or health monitoring, for example, is on the order of seconds to minutes, so the performance achieved even in subthreshold is more than adequate. A very common technique used in microsensor nodes is the duty cycle or shutdown of unused components whenever possible. Although duty cycling helps to extend sensor network lifetimes, it does not remove the energy constraint placed by the power source. Energy harvesting techniques are a necessity in these applications because, if a battery is used instead, it is not possible to recharge or replace batteries frequently. Thus, microsensor networks are a very interesting platform that showcases the need for new low-energy design techniques, which must be applied in the analog and digital domains. This is evident also from Figure 10.1, where a classical mixed-signal system can be easily identified.

#### 10.2.2 Radio Frequency Identification (RFID)

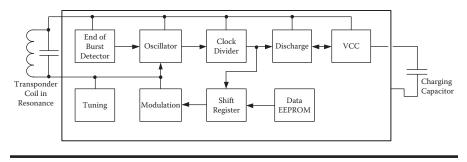

RFID is another typical application that requires extremely low energy consumption [4] [5]. RFID is used to automatically identify objects through RFID tags that are attached to the object. The RFID tag is able to transmit and receive information wirelessly using radio frequencies. An RFID tag contains a limited amount of digital processing logic along with an antenna and communication circuits.

There are two main types of RFID tags. An *active* RFID tag communicates with the reader by transmitting data. Active tags frequently require a power source to supply the energy for transmission, and any extra energy saved due to application of low-power design techniques could be used for extended processing and longer range of communication. A *passive* RFID tag communicates with the reader by modulating the load that the reader sees. This means of communication requires less energy, so passive tags often operate on energy that is converted from the

Figure 10.2 Typical block diagram of an RFID tag.

received signal. Passive nodes are usually smaller as a result, and their lifetimes are not limited by energy.

Reducing power consumption and using energy harvesting would benefit both types of tags. This is straightforward for active tags where minimizing the power consumption leads to both increased transmission range and/or longer battery lifetimes. For passive tags, the power is constrained by the ability to utilize the converted energy from the antenna. If the digital logic power dissipation could be reduced and the system could be assisted from an extra energy source, then the distance from the reader to the tag could increase because less transmitted power has to reach the tag.

As is indicated in Figure 10.2, an RFID tag is comprised of several analog and digital parts, which constitute a mixed-signal environment. To this end, if true low power is to be achieved, the reduction of power consumption of analog and digital parts of the system must be addressed.

#### 10.3 Low Power Techniques in Digital Design

Average power consumption in digital CMOS circuits is more important than peak power as instances of peak power consumption when all the circuit components are on is rare. Ideally, CMOS gates consume power when the output node makes a switching transition. However, there are short circuit and leakage currents through the device that result in wasteful power dissipation. The average power  $P_{avg}$  consumed by a CMOS circuit can be represented mathematically as:

$$P_{avg} = P_{switch} + P_{ShortCkt} + P_{lkg}$$

=  $(C_L \cdot V_{SWING} \cdot V_{DD} \cdot f_{CLK} \cdot \alpha) + (I_{ShortCkt} \cdot V_{DD}) + (I_{lkg} \cdot V_{DD})$  (10.1)

The first term on the right-hand side of equation (10.1), i.e., switching power  $P_{switch}$ , represents the power consumed by the switching capacitance or load

capacitance  $C_L$  of the CMOS circuit. This is the power consumed in charging the load capacitance when the device makes a 0 to 1 transition. It represents approximately 60 to 70 percent [1] of total power consumed. Besides  $C_L$ , switching power is also a function of the supply voltage  $V_{DD}$ , the voltage difference between logic 1 and logic 0  $V_{SWING}$ , the clock frequency  $f_{CLK}$ , and the node transition activity factor  $\alpha$ .  $V_{SWING}$  usually equals the supply voltage  $V_{DD}$ , but for internal nodes, it could be less than  $V_{DD}$ .

The second term of equation (10.1), the short circuit power  $P_{ShortCkt}$ , refers to the power dissipated due to the direct path short circuit current  $I_{ShortCkt}$ , through the PMOS (p-type MOS) and NMOS (n-type MOS) transistors of static logic circuits during a switching transition. It accounts for 20 percent of total power dissipated in static circuits as there is no short circuit current for dynamic design because of precharging. The short circuit current is a function of the rise and fall time of the input and output signals, amount of capacitive load, size of the CMOS devices, and the gate capacitance, especially the equivalent gate to drain capacitance [6].

The last term in equation (10.1) corresponds to power dissipated due to leakage current  $I_{lkg}$ . Usually, leakage current accounts for approximately 2 to 3 percent of the total power. Though, ideally, no power is consumed when both PMOS and NMOS transistors are off, power due to  $I_{lkg}$  arises from inherent reverse biased diode currents  $I_{lkg}$  and subthreshold effects  $I_{subikg}$  of the transistors. The leakage current is strongly a function of the fabrication technology.

Although power consumption is generally considered as a term identical to that of energy consumption, it is worthwhile to notice a fundamental difference in the case of digital circuits. The power consumed by a device is by definition the energy consumed by unit time. In other words, the energy (*E*) required for a given operation is the integral of the power (*P*) consumed over the operation time ( $T_{op}$ ), hence:

$$E = \int_{0}^{T_{op}} P(t) dt \qquad (10.2)$$

If we substitute P(t) in equation (10.2) by the switching power of a digital circuit, which is the main component of the total power consumption  $P_{switch}$  and we assume that an operation requires *n* clock cycles,  $T_{op}$  can be expressed as *n*/*f* and so we get:

$$E = n \cdot C_L \cdot V_{SWING} \cdot V_{DD} \cdot \alpha \tag{10.3}$$

It is important to note that the energy per operation is independent of the clock frequency. Reducing the frequency will lower the power consumption, but will not change the energy required to perform a given operation. Since the energy

consumption is what determines the battery life, it is imperative to reduce the energy rather than just the power. It is, however, important to notice that the power is critical for heat dissipation considerations.

#### 10.3.1 Reducing Power in Digital Circuits

Because switching power accounts for the major portion of the power consumed, any attempt at low-power design should try to minimize it. To this end, low-power design methodologies [7] [8] at every level should aim at reducing the variables in that term, namely,  $C_L$ ,  $V_{DD}$ ,  $V_{swing}$ ,  $f_{clk}$ , and a. However, significant reduction of the power consumption can occur through the following interventions:

- 1. Supply Voltage V<sub>DD</sub> Reduction: Power consumed by a CMOS device is proportional to the square of the supply voltage  $V_{DD}$  and, hence, lowering the supply voltage would result in a quadratic reduction in power consumption, though device current reduces only linearly with V<sub>DD</sub>. It can be proved that in this way the power can be practically reduced by one to eight times [9]. Supply reduction can be achieved through some special circuit manipulations and through feature size scaling, but the designer must be very careful because often these techniques impose serial limitations, such as circuit delay and degraded functional throughput. For computationally intensive functions, one of the effective ways to reduce power consumption while still operating at low voltage is to parallelize the computation by modifying the algorithm and the architecture. The key to architecture-driven voltage scaling is to exploit concurrency (pipelining and parallelism) in execution. Also, the combination of architectural optimization with threshold voltage reduction can scale down supply voltage to the sub-1 V range. To compensate for the loss in speed due to voltage scaling, it is possible to upsize the transistors that are in the critical delay path, or by transistor sizing, using fast logic structures [10].

- 2.  $V_{swing}$  Reduction: Power consumption of a CMOS logic gate with a fixed supply voltage  $V_{DD}$  also can be reduced by restricting the voltage swing  $V_{swing}$  at the output node [10] [11]. Usually, the output node of the gate will make rail-to-rail transitions ( $V_{DD}$  to 0 or 0 to  $V_{DD}$ ). But, if an NMOS device has been used instead as a pull up, the output will limit the swing to ( $V_{DD} V_T$ ). The power consumed for a 0 to ( $V_{DD} V_T$ ) in such a case will be  $C_L \cdot V_{DD} \cdot (V_{DD} V_T)$ , and the reduction in power consumption (over a rail-to-rail scheme) is proportional to  $V_{DD} / (V_{DD} V_T)$ . However, there are a few drawbacks with such a design, such as the reduced noise margin and increased power consumption at the subsequent stage [12].

- 3. Load Capacitance ( $C_L$ ) Reduction: An obvious way to reduce the load capacitance is to reduce the CMOS device size since scaling reduces the channel and parasitic capacitance [12]. Logic/circuit minimization through effective partitioning can also reduce the load capacitance.

4. Node Transition Activity α Reduction: Switching activity reduction can help to reduce power consumption in CMOS devices as power is consumed only during transitions. Various techniques range from simply powering down the complete circuit or portions of it, to more sophisticated schemes in which the clocks are gated or optimized circuit architectures are used that minimize the number of transitions [13]. An important attribute that can be used in circuit and architectural optimization is the correlation in the temporal sequence of data because switching should decrease if the data are slowly changing, i.e., highly positively correlated. Thus, knowledge about signal statistics can be used to reduce the number of transitions. The techniques for a reduction span all levels of the system design from the physical design level, to the logic level where logic minimization and logic level power down are the key techniques to minimize the transition activity [13].

Though switching power accounts for the major share of the total power dissipated, short circuit and leakage power usually amount to 20 to 30 percent. In order to reduce short circuit power, gate capacitances, device size, and the rise and fall time of the signals should be reduced. Leakage power, on the other hand, can be reduced by accurate device modeling and threshold control. The various power-reducing parameters discussed can be optimized at various design levels to a different extent.

#### 10.4 Low Power Techniques in Analog Design

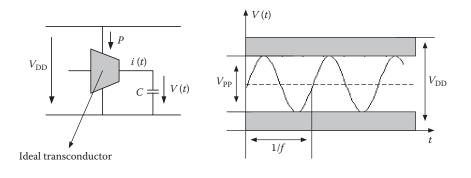

Power is consumed in analog signal processing circuits to maintain the signal energy above the fundamental thermal noise in order to achieve the required signal-to-noise ratio (SNR). A representative figure of merit of different signal processing systems is the power consumed to realize a single pole. The minimum power necessary to realize a single pole can be derived by considering the basic integrator presented in Figure 10.3 where an ideal 100 percent current efficient transconductor is used, in the sense that all the current pulled from the supply voltage is used to charge the integrating capacitor [14].

The power consumed from the supply voltage source  $V_{DD}$  that is necessary to create a sinusoidal voltage V(t) across capacitor C having peak-to-peak amplitude  $V_{PP}$  and frequency f can be expressed as:

$$P = V_{DD} \cdot fCV_{PP} = fCV_{PP}^2 \cdot \frac{V_{DD}}{V_{PP}}$$

(10.4)

and the signal-to-noise ratio is given by:

$$SNR = \frac{V_{PP}^2/8}{kT/C}$$

(10.5)

#### Figure 10.3 An ideal, single-pole analog processing filter.

Combining equation (10.4) and equation (10.5), we get:

$$P = 8kT \cdot f \cdot SNR \cdot \frac{V_{DD}}{V_{PP}}$$

(10.6)

According to equation (10.6), the minimum power consumption of analog circuits at a given temperature is basically set by the required SNR and the frequency of operation (or the required bandwidth). Since this minimum power consumption is also proportional to the ratio between the supply voltage and the signal peak-to-peak amplitude, power efficient analog circuits should be designed to maximize the voltage swing. The minimum power per pole for circuits that can handle rail-to-rail signal voltages ( $V_{PP} = V_{DD}$ ) reduces to [15]–[18]:

$$P_{MIN} = 8kT \cdot f \cdot SNR \tag{10.7}$$

This absolute limit is very steep because it requires a factor 10 of power increase for every 10 dB of signal-to-noise ratio improvement. It applies to each pole of any linear analog filter (continuous and sampled data [19]) and is reached in the case of a simple passive RC (resistor-capacitor) filter, whereas the best existing active filters consume about two orders of magnitude more power per pole. High Q poles in the passband reduce the maximum signal amplitude at other frequencies and, therefore, increase the required power, according to equation (10.6).

Approximately the same result is found for relaxation oscillators, whereas the minimum power required for a voltage amplifier of gain  $A_v$  can be proved to be always larger or equal to:

$$P_{MIN} = 8nkT \cdot \Delta f \cdot A_V \cdot SNR \tag{10.8}$$

which mean that is again proportional to SNR and is  $n \times A_v$  times larger than the limit given by equation (10.7).

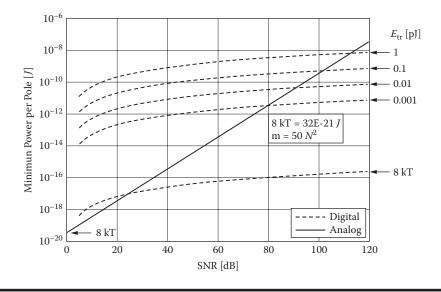

#### 10.5 Comparison of the Power Consumption of Analog and Digital Circuits

The minimum power for an analog system can be compared to that of a digital system, which, if the transistors are considered ideal, corresponds to the switching component  $P_{Switch}$  of equation (10.1), i.e.:

$$P_{\min-digital} = C_L \cdot V_{SWING} \cdot V_{DD} \cdot f_{CLK} \cdot \alpha$$

=  $P_{\min-digital} = E_t \cdot f_{CLK} \cdot \alpha$  (10.9)

In equation (10.9), each elementary operation requires a certain number of binary gate transition cycles, each of which dissipates an amount of energy  $E_{tr}$ . Due to the Nyquist theorem,  $f_{CLK}$  must be at least twice the signal bandwidth so  $f_{CLK}$  can be considered to be the signal bandwidth if we account a factor (1/2) into the constant  $E_{tr}$ .

The number m of transitions is only proportional to some power m of the number of bits N, and, therefore, power consumption is only weakly dependent on SNR (essentially logarithmically) [20]:

$$a = N^m \approx [\log(SNR)^m] \tag{10.10}$$

Comparison with analog is obtained by estimating the number  $\alpha$  of gate transitions that are required to compute each period of the signal, which for a single pole digital filter can be estimated to be approximately:

$$a \cong 50 \cdot N^2 \tag{10.11}$$

From equation (10.9),  $E_{tr} = C_L \cdot V_{SWING} \cdot V_{DD} = C_L \cdot V_{DD}^2$ , which varies from 10<sup>-12</sup> to 10<sup>-15</sup> Joule.

Combining equation (10.9) to equation (10.11), we get:

$$P_{\min-digital} \cong E_{tr} \cdot f_{CLK} \cdot 50 \cdot [\log(SNR)]^2$$

(10.12)

Therefore, the relationship between switching energy and signal-to-noise ratio (S/N) is logarithmic. Comparison of analog and digital fundamental limits is depicted in Figure 10.4, and clearly shows that analog systems may consume much less power than their digital counterparts, provided a small signal-to-noise ratio is acceptable. But, for systems requiring large signal-to-noise ratios, analog becomes very power-inefficient.

Figure 10.4 Minimum power consumption of analog and digital circuits.

#### 10.6 Combination of Techniques Toward Low-Voltage, Mixed-Signal Design

Unlike digital circuits where, according to equation (10.3), the power consumption decreases with the square of the supply voltage, reducing the supply voltage of analog circuits while preserving the same bandwidth and SNR has no fundamental effect on their minimum power consumption. However, this absolute limit was obtained by neglecting the possible limitation of bandwidth *BW* due to the limited transconductance  $g_m$  of the active device. The maximum value of *BW* is proportional to  $g_m/C$ . Replacing the capacitor value *C* by  $g_m/BW$  in equation (10.5) and expressing the product of the *SNR* times the bandwidth yields:

$$SNR \cdot BW = \frac{V_{pp}^2 \cdot g_m}{8kT}$$

(10.13)

In most of the cases, scaling the supply voltage  $V_{DD}$  by a factor K requires a proportional reduction of the signal swing  $V_{pp}$ . Maintaining the bandwidth and the SNR, therefore, is only possible if the transconductance  $g_m$  is increased by a factor  $K^2$ . If the active device is a bipolar transistor (or a MOS transistor biased in subthreshold region), its transconductance can only be increased by increasing the bias current I by the same factor  $K^2$  and, therefore, power  $V_{DD} \cdot I$  is also increased by K.

The situation is different if the active device is a MOS transistor biased in strong inversion. Its transconductance can be shown to be proportional to  $I/V_P$ , where  $V_P$  is the pinch off or saturation voltage of the device. Because this saturation voltage also has to be reduced proportionally with  $V_{DD}$ , then increasing  $g_m$  by  $K^2$  only requires an increase of current by a factor K and, hence, the power remains unchanged. However, even in this case, supply reduction has serious effects on the functionality of the circuit, since it affects the maximum frequency of operation. For a MOS transistor in strong inversion, the frequency  $f_{max}$ , for which the current falls to unity, is given by approximately:

$$f_{\max} = \frac{\mu \cdot V_P}{L^2} \tag{10.14}$$

Therefore, if the process is fixed (channel length *L* constant), a reduction of  $V_{DD}$  and  $V_P$  by a factor *K* causes a proportional reduction of  $f_{max}$ .

Reduction of the supply voltage also has an implicit effect on the dynamic range of the analog processor. The *dynamic range* (DR) of an ideal integrator, such as this of Figure 10.3, is given by [20]:

$$DR_{\max} = \frac{CV_{DD}^2}{8kT}$$

(10.15)

Therefore, implementation of an analog signal processing circuit with a specific dynamic range, in an environment of low-supply voltage, poses an additional challenge for the analog designer.

Unfortunately, in analog systems, low-voltage limitations are not restricted to power or frequency problems. For example, reducing  $V_p$  also increases the transconductance-to-current ratio of MOS transistors that, in turn, increases the noise content of current sources, decreasing SNR this way, while at the same time it drastically degrades their precision.

#### 10.7 Optimum Combination of Analog and Digital Low-Power Techniques

As is evident from the above, the main tool that a designer has toward lowering the power consumption of a digital circuit, namely the voltage supply reduction, is not so effective in analog design because power consumption of analog circuits is mainly dependent on SNR, and voltage supply usually leads to an increase of power consumption.

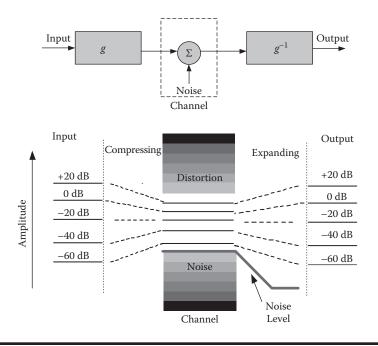

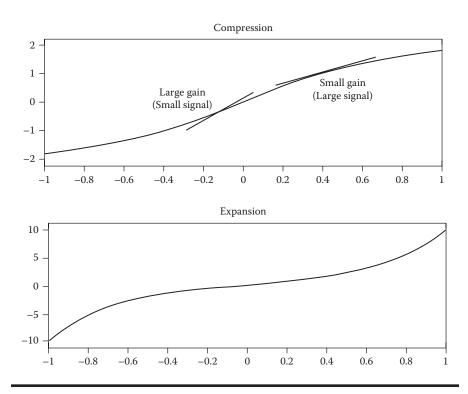

#### 10.7.1 Instantaneous Companding Technique

A possible way to maintain a sufficient dynamic range when reducing the supply voltage, without degrading the power consumption of analog signal processing circuits, is to use the instantaneous companding technique [21]–[23]. In this approach, the currents are compressed when transformed into voltages and expanded when transformed back to currents. The input current has to be predistorted in order to preserve a linear operation.